杮島嵗乮Building My Very First Tube Amp島嵗乯偱偼丄扤偱傕斾妑揑梕堈偵慡抜嵎摦僾僢僔儏僾儖丒傾儞僾偑惢嶌偱偒傞傛偆偵偡傞偨傔偵丄俀抜嵎摦峔惉偺愝寁傪婎杮偲偟偰榖傪偡偡傔偰偒傑偟偨丅偟偐偟丄懡偔偺曽偑弶嶌偺俁抜峔惉偺乽6AH4GT慡抜嵎摦PP傾儞僾乿偵嫮偄娭怱傪帩偭偰偄傜偭偟傖偄傑偡丅俀抜峔惉偺昗弨傾儞僾偼丄偪傚偭偲岺晇偡傞偙偲偱俁抜峔惉壔偑壜擻偱偁傞偙偲傕愜傝偵怗傟偰徯夘偟偰偒傑偟偨偑丄偙傟傑偱側偐側偐偙偺僥乕儅偵偮偄偰嬶懱揑側儁乕僕傪嶌傟側偄偱偄傑偟偨丅偄偊丄偨偩巹偑偝傏偭偰偄偨偩偗側傫偱偡偑丄偄偮傑偱傕曻偭偰偍偔傢偗偵偼備偒傑偣傫偟丄宖帵斅偱俁抜峔惉壔偺榖戣傕弌偨偙偲側偺偱傂偲偮婃挘偭偰傒傞偙偲偵偟傑偟偨丅

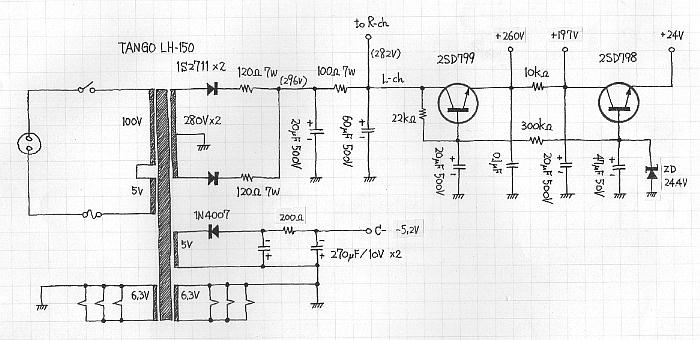

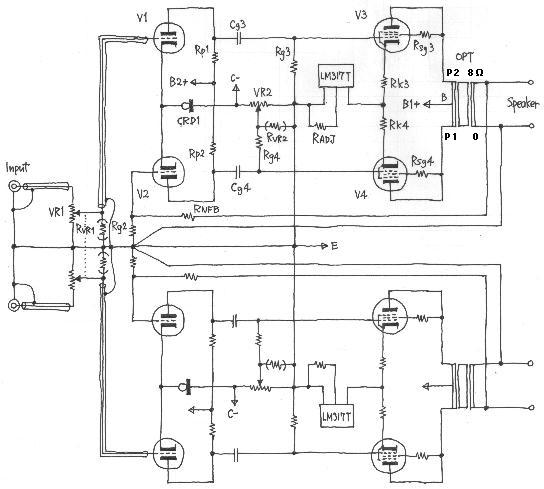

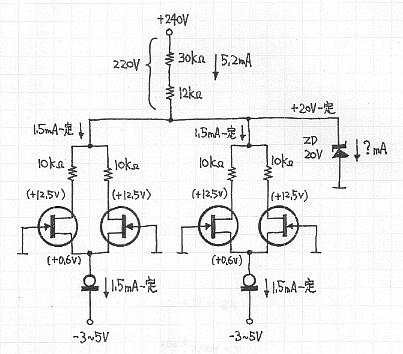

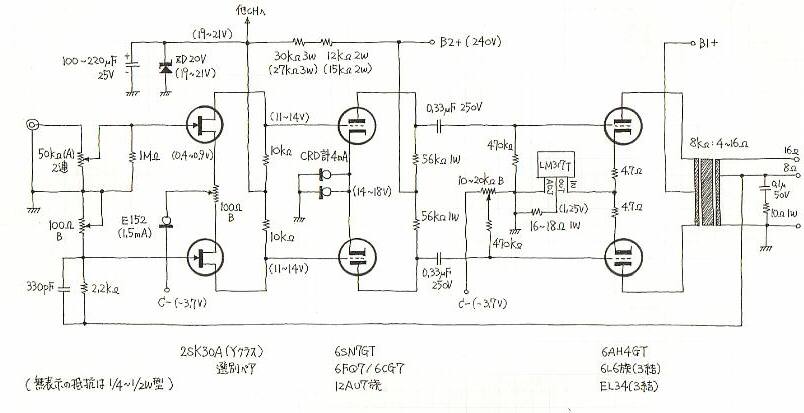

塃恾偼丄杮僾儘僕僃僋僩偱愝寁丒惢嶌偟偨俀抜峔惉偺慡抜嵎摦僾僢僔儏僾儖丒傾儞僾偺婎杮夞楬偱偡丅

塃恾偼丄杮僾儘僕僃僋僩偱愝寁丒惢嶌偟偨俀抜峔惉偺慡抜嵎摦僾僢僔儏僾儖丒傾儞僾偺婎杮夞楬偱偡丅

弶抜侾抜偱弌椡抜偺僪儔僀僽偵昁梫側棙摼傪壱偄偱偄傑偡丅偦偺偨傔偵丄弶抜偱偼棙摼偑壱偘傞崅兪揹埑憹暆娗偺6SL7GT傗6SC7丄偁傞偄偼12AX7傪巊梡偟傑偡丅偙偺傛偆側媴偼堦斒偵撪晹掞峈偑崅偔丄偟偐傕彮側偄僾儗乕僩揹棳乮儀乕僔僢僋丒傾儞僾偱偼0.5mA亊2乯偱偺摦嶌偵側傝傑偡丅偦偺偨傔偵丄僾儗乕僩晧壸掞峈傕200k兌慜屻偺崅掞峈偵側傝傑偡丅

弶抜偺弌椡僀儞僺乕僟儞僗偑崅偄偨傔丄弌椡抜偺擖椡梕検偲偱寛掕偝傟傞崅堟偺帪掕悢乮亖廃攇悢摿惈偑尭悐偟偼偠傔傞億僀儞僩乯偼戝偒偔側傝乮亖掅偄廃攇悢偵側傝乯傑偡丅偙傟偑俀抜峔惉偵偍偗傞庛揰偺傂偲偮偱丄嵎摦僾僢僔儏僾儖丒傾儞僾偵尷傜偢丄崅兪揹埑憹暆娗乮俆嬌娗傪娷傓乯偱僪儔僀僽偡傞俀抜峔惉偺僔儞僌儖丒傾儞僾偱傕摨偠栤戣偑惗偠傑偡丅

偪側傒偵丄弌椡抜偺擖椡梕検偲偼丄僪儔僀僶抜偐傜傒傞偲梕検晧壸乮亖僐儞僨儞僒乯偲偟偰擣幆偝傟傑偡丅偮傑傝丄僪儔僀僶抜偺弌椡僀儞僺乕僟儞僗偲弌椡抜偺擖椡梕検偲偱峔惉偝傟傞儘乕丒僷僗丒僼傿儖僞乕偑偱偒傞傢偗偱偡丅

擖椡梕検偺徻嵶偵偮偄偰偼丄偙偺儁乕僕偺乽恀嬻娗偺擖椡梕検丒丒丒Ck偲Cg-p乿偺復傪嶲徠偟偰偔偩偝偄丅

偙偺栤戣傪夝寛偡傞偵偼丄僪儔僀僶抜偺弌椡僀儞僺乕僟儞僗傪壓偘傞偺偑嵟傕岠壥揑偱偡丅6SL7GT傪巊梡偟偨帪偺弌椡僀儞僺乕僟儞僗偼40k兌慜屻偵側傝傑偡偑丄掅兪丒掅撪晹掞峈偺6SN7GT偱偼8k兌慜屻傑偱壓偘傞偙偲偑偱偒傑偡丅弌椡僀儞僺乕僟儞僗偑1/5偵側傞偲偄偆偙偲偼丄崅堟偺廃攇悢摿惈偑尭悐偟偼偠傔傞億僀儞僩傪5攞傕崅偄廃攇悢偵偱偒傞偲偄偆偙偲偱偡丅

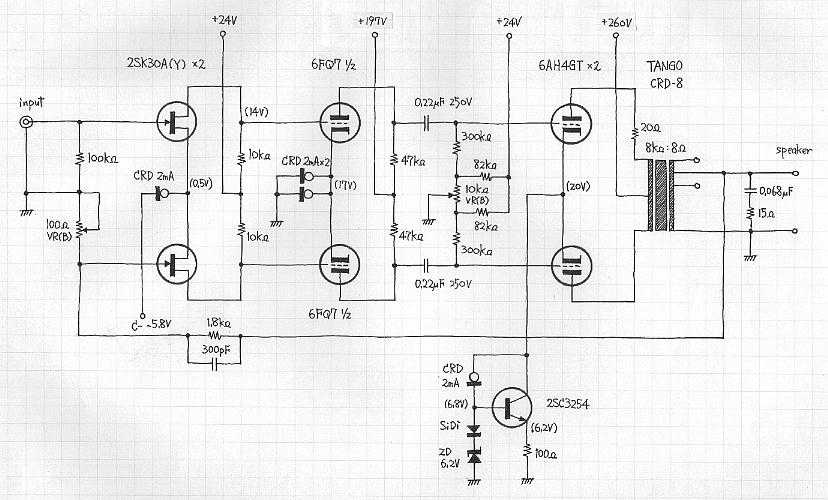

壓恾偼丄弶嶌偺俁抜峔惉偺6AH4GT慡抜嵎摦PP傾儞僾偺傾儞僾晹偺夞楬偱偡丅弶抜偼丄僆乕僨傿僆梡FET偲偟偰旕忢偵億僺儏儔乕側2SK30A偵傛傞嵎摦夞楬偱偡丅FET偼恀嬻娗偺俆嬌娗偵旕忢偵椙偔帡偨摿惈傪帩偭偨敿摫懱偱丄恀嬻娗偱偄偆僌儕僢僪偵偁偨傞傕偺傪僎乕僩乮G乯偲屇傃丄僇僜乕僪偵偁偨傞傕偺傪僜乕僗乮S乯丄僾儗乕僩偵偁偨傞傕偺傪僪儗僀儞乮D乯偲屇傃傑偡丅恀嬻娗偲摨條偵僎乕僩偵儅僀僫僗偺僶僀傾僗傪梌偊偰摦嶌偝偣傑偡丅

嵎摦夞楬偱偡偺偱丄嫟捠僜乕僗懁偼2mA偺掕揹棳僟僀僆乕僪乮CRD乯偱掕揹棳壔偝傟偰偄傑偡丅廬偭偰丄侾屄偺FET偁偨傝偺僪儗僀儞揹棳偼1mA偱偡丅揹尮揹埑偼24V偱丄僪儗僀儞晧壸掞峈偼10k兌偱偙偙偵1mA偑棳傟偰偄傑偡偐傜丄10k兌偵偍偗傞揹埑崀壓偼10V偲側傝丄僪儗僀儞揹埑偼24V亅10V亖14V偵側傝傑偡丅

弶抜僪儗僀儞偼師抜乮亖僪儔僀僶抜乯偺僌儕僢僪偲捈寢偵側偭偰偄傑偡丅僪儔僀僶抜偼掅撪晹掞峈丄掅兪偺6FQ7偑巊傢傟偰偍傝丄偙傟傕嵎摦夞楬偵側偭偰傑偡丅嫟捠僇僜乕僪懁偵2mA偺掕揹棳僟僀僆乕僪偑俀杮暲楍偵偼偄偭偰偄偰崌寁4mA偺掕揹棳夞楬偵側偭偰偄傑偡丅偙偺摦嶌忦審偱偼丄僪儔僀僶抜偺僶僀傾僗偼栺3V亄兛偔傜偄偵側傝丄傾乕僗偵懳偟偰17V偔傜偄偵側傝傑偡丅奺抜偺摦嶌忦審偍傛傃儘乕僪儔僀儞偼偙偪傜偺儁乕僕傪嶲徠偟偰偔偩偝偄丅

弶抜偺擖椡偲斀懳懁偺2SK30A偺僎乕僩偵偼僗僺乕僇抂巕偐傜偺僆乕僶乕僆乕儖偺晧婣娨偑偐偗傜傟偰偄傑偡丅晧婣娨慺巕偼丄300pF偺僐儞僨儞僒傪書偐偣偨1.8k兌偺掞峈偱偡丅偙偺300pF偼偄傢備傞乽埵憡曗惓梡僐儞僨儞僒乿偲偄偆傕偺偱丄偙傟偑側偄偲100kHz埲忋偺挻崅堟偱廃攇悢摿惈偵僺乕僋傪惗偠偰偟傑偄丄攇宍偑峳傟偰偒傑偡丅俁抜峔惉偺傾儞僾偵偍偗傞晧婣娨偺擄偟偄偲偙傠偱偡丅

偙偺傾儞僾偼揹尮夞楬偵偐側傝庤偑偐偐偭偰偍傝丄偲偄偆傛傝夁忚搳帒婥枴側偲偙傠偑偁傝傑偡丅崅懴埑僩儔儞僕僗僞乮2SD799乯偵傛傞儕僾儖丒僼傿儖僞偵壛偊偰弶抜傕僩儔儞僕僗僞乮2SD798乯偑巊傢傟偰偍傝丄偙偪傜偺曽偼24V偺僣僃僫丒僟僀僆乕僪傪暪梡偟偨掕揹埑揹尮偵側偭偰偄傑偡丅偟偐傕丄偙傟偑嵍塃俀杮棫偰偵側偭偰撈棫偟偰偄傑偡丅乮壓恾乯

幚偼偙偆側偭偨偺偵偼栿偑偁傝傑偡丅巊梡偟偨揹尮僩儔儞僗偺俛揹尮梡俀師姫偒慄偺揹埑偑嵟傕掅偄僞僢僾偱傕280V偲崅偡偓偨偐傜偱偡丅斾妑揑掅偄揹尮揹埑偵側偠傓6AH4GT傪巊偆偵偼丄彮乆嫮堷偱傕揹尮揹埑傪僪儘僢僾偝偣側偗傟偽側傜偢丄僪儘僢僾偝偣偨偙偲偱惗偠傞擬傪暘嶶偝偣偰摝偑偡偨傔偵偙偺傛偆側戝妡偐傝側揹尮夞楬偵側偭偨偲偄偊傑偡丅尰幚揑偵偼偙偙傑偱傗傞昁梫偑側偄偺偼丄崱夞惢嶌偟偨昗弨傾儞僾偱徹柧嵪傒偱偡丅

俁抜峔惉偵偍偗傞弶抜摦嶌忦審偺愝寁

昗弨僔儍乕僔傪巊偭偨俀抜峔惉偺慡抜嵎摦PP傾儞僾傪俁抜峔惉壔偟傛偆偲偡傞偲恀嬻娗梡偺寠偑懌傝側偔側傝傑偡丅昗弨僔儍乕僔偵奐偗傜傟偨恀嬻娗梡偺寠偼慡晹偱俇屄偟偐偁傝傑偣傫丅婃忎側僗僠乕儖惢僔儍乕僔偵戝寠傪奐偗傞偵偼偐側傝嫮椡側岺嬶偲暲奜傟偨擡懴偑偄傝傑偡偑丄偦傫側偙偲傪偡傞偮傕傝偼偝傜偝傜偁傝傑偣傫偺偱丄弶抜偵偼弶嶌摨條偵敿摫懱乮FET乯傪巊偆偙偲偵偟偰僐儞僷僋僩偵傑偲傔傞偙偲偵偟傑偡丅

昗弨僔儍乕僔傪巊偭偨俀抜峔惉偺慡抜嵎摦PP傾儞僾傪俁抜峔惉壔偟傛偆偲偡傞偲恀嬻娗梡偺寠偑懌傝側偔側傝傑偡丅昗弨僔儍乕僔偵奐偗傜傟偨恀嬻娗梡偺寠偼慡晹偱俇屄偟偐偁傝傑偣傫丅婃忎側僗僠乕儖惢僔儍乕僔偵戝寠傪奐偗傞偵偼偐側傝嫮椡側岺嬶偲暲奜傟偨擡懴偑偄傝傑偡偑丄偦傫側偙偲傪偡傞偮傕傝偼偝傜偝傜偁傝傑偣傫偺偱丄弶抜偵偼弶嶌摨條偵敿摫懱乮FET乯傪巊偆偙偲偵偟偰僐儞僷僋僩偵傑偲傔傞偙偲偵偟傑偡丅

弶抜偺摦嶌忦審偱偡偑丄FET偵偼擖庤梕堈側2SK30A傪巊偄丄揹尮揹埑偼栺20V丄掕揹棳尮偼1.5mA慜屻偲偟傑偡丅2SK30A偼Y僋儔僗傪憐掕偟傑偡偑丄GR僋儔僗偱傕幚幙揑偵偼塭嬁偁傝傑偣傫丅弶抜揹尮夞楬傪僔儞僾儖偵偡傞偨傔偵慡徚旓揹棳傪彮偟梷偊栚偵偟傑偟偨乮屻偱徻愢偟傑偡乯丅2SK30A侾杮偁偨傝偺僪儗僀儞揹棳偼0.75mA慜屻傪憐掕偟傑偡丅僪儗僀儞晧壸掞峈偼10k兌偱偡丅

偙偺忦審偱2SK30A偺摿惈僨乕僞偵儘乕僪儔僀儞傪堷偄偰傒偨偺偑塃恾偱偡丅儘乕僪儔僀儞乮10k兌乯忋偱Id亖0.75mA偵側傞億僀儞僩偑摦嶌揰偱偡丅僶僀傾僗偼FET偺偽傜偮偒偺偣偄偱-0.4乣-0.9V偺偳偙偐偵側傝傑偡偺偱丄偦偺偙偲傪尒墇偟偰儘乕僪儔僀儞偼Ed亖19.4V偁偨傝偐傜堷偄偰偁傝傑偡丅廬偭偰丄僪儗僀儞揹埑偼11.9V偔傜偄偵側傝丄偙傟偑僪儔僀僶抜偺僌儕僢僪偲捈寢偝傟傑偡丅

偙偺億僀儞僩偵偍偗傞gm抣偼偩偄偨偄1.6偔傜偄側偺偱丄弶抜棙摼偼丄1.6亊10k兌亖16攞偲憐掕偝傟傑偡丅乮嶲峫僨乕僞丗2SK30A gm幚應僨乕僞乯

俁抜峔惉偵偍偗傞僪儔僀僶抜摦嶌忦審偺愝寁

俀抜峔惉偺慡抜嵎摦PP傾儞僾偱偼丄棙摼傪壱偖偨傔偵兪偑崅偄6SL7GT偁傞偄偼6SC7傪巊偄傑偟偨偑丄俁抜峔惉壔偡傞応崌偼媡偵棙摼偑崅偔側傝偡偓傞偺偱丄僪儔僀僶抜偵偼兪偑掅偄媴傪慖偽側偗傟偽側傝傑偣傫丅偲偼偄偭偰傕US8僺儞儀乕僗偱兪偑掅偄憃俁嬌娗偱擖庤梕堈側媴偲偄偆偲6SN7GT偔傜偄偟偐慖戰巿偑偁傝傑偣傫丅

俀抜峔惉偺慡抜嵎摦PP傾儞僾偱偼丄棙摼傪壱偖偨傔偵兪偑崅偄6SL7GT偁傞偄偼6SC7傪巊偄傑偟偨偑丄俁抜峔惉壔偡傞応崌偼媡偵棙摼偑崅偔側傝偡偓傞偺偱丄僪儔僀僶抜偵偼兪偑掅偄媴傪慖偽側偗傟偽側傝傑偣傫丅偲偼偄偭偰傕US8僺儞儀乕僗偱兪偑掅偄憃俁嬌娗偱擖庤梕堈側媴偲偄偆偲6SN7GT偔傜偄偟偐慖戰巿偑偁傝傑偣傫丅

僪儔僀僶抜偺摦嶌忦審偼丄揹尮揹埑偼栺240V丄掕揹棳尮偼4mA慜屻偲偟傑偡丅6SN7GT偺Ep-Ip摿惈偼6FQ7偲摨摍側偺偱庤尦偵偁傞6FQ7偺幚應Ep-Ip僨乕僞傪棳梡偟傑偡丅揹尮揹埑偼240V偱傕儘乕僪儔僀儞傪堷偔帪偵偼224V偔傜偄偺忦審偱堷偒傑偡丅側偤偐偲偄偆偲丄弶抜偲捈寢偵偡傞偨傔偵僇僜乕僪揹埵偑16V偔傜偄偵側偭偰偟傑偆偐傜偱偡丅僾儗乕僩晧壸掞峈偼56k兌偲偟偰傒傑偡丅

偙偺忦審偱6SN7GT乮亖6FQ7乯偺摿惈僨乕僞偵儘乕僪儔僀儞傪堷偄偰傒偨偺偑塃恾偱偡丅儘乕僪儔僀儞乮56k兌乯忋偱Ip亖2mA偵側傞億僀儞僩偑摦嶌揰偱偡丅僾儗乕僩揹埑偼112V丄僶僀傾僗偼偍偍傛偦-4V偵側傝傑偡丅僾儗乕僩揹棳偑2mA偲傗傗彮側傔側偺偼丄慡徚旓揹棳傪愡栺偟偰偄傞偨傔偱偡丅傕偭偲傕丄偙偺揹棳傪偆傫偲憹傗偟偨偐傜偲偄偭偰壒偑偳偆側傞偲偄偆傕偺偱傕偁傝傑偣傫丅

弶抜偺儘乕僪儔僀儞偺帪偼晧壸掞峈偺儘乕僪儔僀儞侾杮偩偗偱偟偨偑丄僪儔僀僶抜偼弌椡抜偺僌儕僢僪掞峈乮昗弨傾儞僾偱偼470k兌偔傜偄乯傕暲楍偵晧壸偵側傝傑偡偺偱丄56k兌偲470k兌偺暲楍崌惉抣50k兌亖乮56k兌亊470k兌乯亐乮56k兌亄470k兌乯丄偑僪儔僀僶抜偺恀偺岎棳晧壸偵側傝傑偡丅岎棳晧壸偺儘乕僪儔僀儞偼丄偝偒偵媮傔偨捈棳晧壸偵偍偗傞摦嶌忦審乮僾儗乕僩揹埑亖112V丄僾儗乕僩揹棳亖2mA乯傪捠傞傛偆側孹偒偑-50k兌偺儘乕僪儔僀儞偱偡丅

6SN7GT偺兪抣偼偩偄偨偄20偔傜偄丄撪晹掞峈偼栺10k兌偱偡丅晧壸掞峈偼50k兌偱偡偐傜丄僪儔僀僶抜偺棙摼偼丄20亊乷50k兌亐乮10k兌亄50k兌乯乸亖16.7攞丄偵側傝傑偡丅

6AH4GT傗6L6懓丄EL34偺俁嬌娗愙懕偺応崌丄僶僀傾僗偼-20V乣-25V偔傜偄偺斖埻偩偲巚偄傑偡偺偱丄僪儔僀僶抜偼偐側傝偺梋桾傪傕偭偰弌椡抜傪僪儔僀僽偱偒偰偄傑偡丅偦偺偨傔丄偙偙偱偼僪儔僀僶抜偺揹尮揹埑傪240V偱偁傞偲偟偰寁嶼偟傑偟偨偑丄亇20V偔傜偄偺斖埻偱偁傟偽偙偺傑傑偺掕悢偱傕偐傑偄傑偣傫丅曄壔偡傞偺偼僶僀傾僗偺怺偝偲偦傟偵敽偆僇僜乕僪揹埵偺傢偢偐側曄壔偩偗偱偡丅僾儗乕僩揹棳偼曄傢傝傑偣傫丅婥偵側傞傛偆偱偟偨傜丄偛帺恎偱儘乕僪儔僀儞傪堷偒側偍偟偰丄揔愗側僾儗乕僩晧壸掞峈偁傞偄偼僾儗乕僩揹棳傪慖傫偱偔偩偝偄丅僾儗乕僩晧壸掞峈偼33k兌乣68k兌偔傜偄偺斖埻偺偳傟偱傕偐傑偄傑偣傫丅壒偵梌偊傞僀儞僷僋僩偼旕忢偵彫偝偄偱偡丅

俁抜峔惉偵偍偗傞弶抜揹尮夞楬偺愝寁

偙偙偱偼丄僪儔僀僶抜偵嫙媼偡傞揹尮揹埑偑240V丄弶抜偑20V偱偁傞偲偟偰愝寁傪恑傔傑偡丅

亙掞峈堦敪偺揹埑僪儘僢僾偼晄壜亜

弶抜偵嫙媼偡傞揹尮揹埑偼20V偲旕忢偵掅偄偺偱掞峈傪巊偭偰僪儘僢僾偝偣傑偡丅偙偙偱拲堄偟側偗傟偽側傜側偄偺偼丄掞峈偩偗偱扨弮偵僪儘僢僾偝偣偰偼偄偗側偄偲偄偆偙偲偱偡丅弶抜FET偺僪儗僀儞揹棳偼掕揹棳僟僀僆乕僪偵傛偭偰堦堄偵寛掕偝傟偰偄傑偡丅偐傝偵1.5mA偩偲偟傑偟傚偆丅240V偐傜20V偵掞峈侾杮偱棊偲偡偨傔偵偼丄乮240V亅20V乯亐1.5mA亖146.7k兌偱偄偄偙偲偵側傝傑偡丅146.7k兌偲偄偆抣偺掞峈婍偼偁傝傑偣傫偐傜150k兌傪巊偆偙偲偵側傞偱偟傚偆丅150k兌偺掞峈婍偵1.5mA偑棳傟傞偲225V偺揹埑崀壓偑惗偠傑偡丅嫙媼揹埑240V偵懳偟偰225V偺揹埑崀壓偱偡偐傜丄摼傜傟傞弶抜揹尮揹埑偼15V偱偡丅側傫偲丄20V偺偼偢偑15V偵側偭偰偟傑偄傑偟偨丅掕揹棳僟僀僆乕僪偺摿惈偑傎傫偺偡偙偟曄壔偟偰傕弶抜揹尮揹埑偼戝偒偔怳傟偰偟傑偄傑偡偟丄240V偑曄摦偟偰傕摨偠栤戣偑惗偠傑偡丅偙偺傑傑偱偼旕忢偵埨掕惈傪寚偄偨夞楬扴偭偰偟傑偄傑偡丅

埨掕搙偺埆偄夞楬偼丄壒偺椙偟埆偟傪塢乆偡傞埲慜偺栤戣偱偡丅晄埨掕偱偁偭偨傝丄埨慡惈偵栤戣偺偁傞夞楬偼嶌偭偰偼偄偗傑偣傫丅僪儘僢僾掞峈偵僣僃僫丒僟僀僆乕僪乮掕揹埑僟僀僆乕僪乯傪侾杮壛偊傞偙偲偱丄晹昳偺偽傜偮偒傗嫙媼揹埑偺曄摦偑偁偭偰傕埨掕偟偨摦嶌偑摼傜傟傞夞楬偵偡傞偙偲偑偱偒傑偡丅

亙愝寁偺億僀儞僩亜

杮夵憿偵偍偗傞揹尮夞楬傪娷傓弶抜偺俢俠摦嶌傪傑偲傔偨偺偑塃恾偱偡丅

侾偮偺嵎摦夞楬偛偲偵1.5mA偺掕揹棳僟僀僆乕僪偑妱傝摉偰偝傟偰偄傞偺偱丄嵎摦夞楬曅僠儍僱儖偁偨傝偺摦嶌揹棳偼忢偵1.5mA偱堦掕偱偡丅揹尮夞楬偼丄曅僠儍僱儖偁偨傝1.5mA偺揹棳偑嫙媼偱偒傟偽懌傝傑偡偺偱僗僥儗僆偱3mA偵側傝傑偡丅乮尰嵼偼1.45mA乣1.75mA偔傜偄偺暆偺Idss抣偺2SK30A傪斝晍偟偰偄傑偡偺偱丄嵟戝3.5mA偱偁傞偙偲傪峫椂偟偰愝寁偝傟傞偙偲傪悇彠偟傑偡乯

俀偮偺嵎摦夞楬偲暲楍偵20V偺僣僃僫丒僟僀僆乕僪乮ZD乯偑偁傞偨傔偵丄弶抜揹尮揹埑偼20V偵側傠偆偲偟傑偡丅240V偺嫙媼揹尮偲僣僃僫丒僟僀僆乕僪偲偺娫偵偼220V偺揹埑嵎偑偁傝傑偡偑丄偙偙偵42k兌乮亖30k兌亄12k兌乯偺掞峈偑偁傞偨傔偵丄42k兌偺掞峈偵偼丄220V亐42k兌亖5.2mA偺揹棳偑棳傟傑偡丅乮5.2mA傛傝傕庒姳懡傔偺揹棳傪棳偡偙偲傪悇彠偟傑偡丅5.7乣5.8mA偔傜偄偑偄偄偱偟傚偆丅廬偭偰夞楬恾偺椺偱偼42k兌偱偼側偔38k兌偔傜偄偵側傞傛偆偵愝寁偟偰偔偩偝偄乯

5.2mA偺偆偪3mA暘偼俀偮偺嵎摦夞楬偵棳傟偰備偒傑偡偑丄2.2mA偑梋偭偰偟傑偄傑偡丅偙偺2.2mA偼僣僃僫丒僟僀僆乕僪偺拞傪棳傟傑偡丅傕偟丄掕揹棳僟僀僆乕僪偺摿惈偵偽傜偮偒偑偁偭偰1.5mA偱偼側偔偰俀偮偲傕1.7mA偩偲偟傑偡丅偙偺応崌丄5.2mA偺偆偪3.4mA偑俀偮偺嵎摦夞楬偵棳傟偰偄偒丄梋偭偨1.8mA偑僣僃僫丒僟僀僆乕僪偺拞傪棳傟傑偡丅僣僃僫丒僟僀僆乕僪偑夞楬偵棳傟傞揹棳偺曄壔傪媧廂偟偰偟傑偆傢偗偱偡偑丄偱偒傟偽1.8mA傛傝傕偆彮偟梋桾偑梸偟偄偺偱丄5.2mA偱偼側偔5.7乣5.8mA傪悇彠偡傞傢偗偱偡丅

5.2mA亅乮CRD揹棳亊2乯亖ZD揹棳240V偺嫙媼揹尮偺揹埑偑260V偵曄摦偟偨傜偳偆側傞偱偟傚偆丅嫙媼揹尮偲僣僃僫丒僟僀僆乕僪偲偺娫偺揹埑嵎偼240V偵側傞偨傔丄42k兌偺掞峈偵偼5.7mA偑棳傟傑偡丅偦偟偰丄5.7mA偺偆偪3mA偼俀偮偺嵎摦夞楬偵棳傟傞偨傔丄巆偭偨2.7mA偑僣僃僫丒僟僀僆乕僪偵棳傟傞傛偆偵側傝傑偡丅偄偢傟偺応崌傕丄僣僃僫丒僟僀僆乕僪偑揹棳偺曄壔傪媧廂偟偰偔傟傞偺偱丄弶抜揹尮揹埑偺20V偼堐帩偝傟傑偡丅

偙偺42k兌偺掞峈偲僣僃僫丒僟僀僆乕僪偺慻傒崌傢偣偼娙堈宆偺掕揹埑揹尮偱丄堦斒偵僔儍儞僩宆掕揹埑夞楬偲偄偄傑偡丅偙偺偟偔傒偺偍偐偘偱丄廃埻偺忦審偺曄壔傗晹昳偺偽傜偮偒偵偐偐傢傜偢丄弶抜揹尮揹埑偼堦掕偵曐偨傟傑偡丅

亙僣僃僫丒僟僀僆乕僪偵偼偳傟偔傜偄偺揹棳傪棳偟偨傜偄偄偐亜

僣僃僫丒僟僀僆乕僪偵棳偡揹棳偼懡偗傟偽懡偄傎偳掕揹埑揹尮偲偟偰偼埨掕偟傑偡偟丄傾儞僾懁偵棳傟傞揹棳偺戝偒偝傗俛揹尮揹埑偺曄摦偵懳偟偰嫮偔側傝傑偡丅僔儍儞僩宆掕揹埑夞楬偱偼丄堦斒偵丄夞楬懁偺徚旓揹棳偲傎傏摨摍偺僔儍儞僩揹棳傪棳偡偺偑僙僆儕乕偱偡偑丄杮婡偱偼偡偙偟帠忣偑堎側傝傑偡丅俀偮偺嵎摦夞楬偵棳傟傞揹棳偼CRD偺偣偄偱堦掕偩偐傜偱偡丅曄摦梫慺偼俀偮丄侾偮偼掕揹棳僟僀僆乕僪偺偽傜偮偒偱丄傕偆侾偮偼俛揹尮揹埑偺曄摦偱偡偑丄掕揹棳僟僀僆乕僪偼慖暿傪峴偆偺偱偽傜偮偒偼娗棟壜擻偱偡丅

偦偺偨傔丄杮愝寁偱偼丄僣僃僫丒僟僀僆乕僪偵棳偡揹棳偑傗傗彮側傔偺2.2mA慜屻偵梷偊偰偁傝傑偡丅偙偺帪偺僣僃僫丒僟僀僆乕僪偺徚旓揹椡偼丄20V亊2.2mA亖44mW偱偡丅偙傟偔傜偄偺徚旓揹椡偱傕暷棻戝偺僣僃僫丒僟僀僆乕僪偵偼壏搙忋徃偑惗偠偰僣僃僫揹埑偼1乣2%忋徃偟傑偡乮仸1乯丅棳偡揹棳傪偁傑傝梸挘傞偲僣僃僫丒僟僀僆乕僪偑崅壏偵側偭偰偟傑偆偺偱拲堄偟偰偔偩偝偄丅

亙掞峈婍偺徚旓揹椡亜

偲偙傠偱丄42k兌偑30k兌偲12k兌偺俀偮偵暘偐傟偰偄傞棟桼偱偡偑丄偦傟偼掞峈婍偺徚旓揹椡偲娭學偑偁傝傑偡丅42k兌偺揹埑僪儘僢僾掞峈偵偼栺5.2mA偺揹棳偑棳傟傑偡偑丄42k兌偺掞峈慡懱偺徚旓揹椡偼丄220V亊220V亐42k兌亖1.15W偵側傝傑偡丅1.15W偺徚旓揹椡傪埨慡偵曻擬偡傞偵偼3W宆偺掞峈婍偱偼偪傚偭偲尩偟偔偰5W宆偑昁梫偱偡乮仸2乯丅偟偐偟丄1k兌埲忋偺掞峈抣傪帩偭偨5W宆僙儊儞僩掞峈偼擖庤偑崲擄偐惢憿偝傟偰偄傑偣傫丅偦偙偱丄庤帩偪偑偁偭偨3W宆偺30k兌偲2W宆偺12k兌偵暘偗偨傢偗偱偡丅1W乣3W宆偼100k兌傑偱側傜梕堈偵庤偵擖傝傑偡丅

偟偐偟丄30k兌3W宆乮徚旓揹椡0.81W乯偲12k兌2W宆乮0.32W乯偺慻傒崌傢偣偼徚旓揹椡僶儔儞僗偑偄傑傂偲偮側偺偱丄怴婯偵晹昳傪挷払偝傟傞偺偱偁傟偽丄27k兌3W宆乮0.73W乯偲15k兌2W宆乮0.41W乯偐傑偨偼24k兌3W宆乮0.65W乯偲18k兌2W宆乮0.49W乯偔傜偄偺慻傒崌傢偣偑偄偄偱偟傚偆丅乮38k兌偲偡傞応崌偼丄22k兌3W宆乮0.74W乯偲16k兌2W宆乮0.54W乯偔傜偄偺慻傒崌傢偣偑偄偄偱偟傚偆丅乯

仸1,2丗偙偺傛偆偵丄揹巕夞楬偱偼屄乆偺晹昳偺徚旓揹椡偲壏搙偺娗棟偑偲偰傕廳梫偱偡丅摿偵丄敿摫懱偼壏搙偵傛偭偰摿惈偑曄壔偡傞偺偑晛捠側偺偱丄崅壏偵側傞傛偆側応崌乮杮婡偱偼峫椂晄梫偱偡乯偵偼丄壏搙摿惈偺専摙傕偟側偗傟偽側傝傑偣傫丅

仸1,2丗偙偺傛偆偵丄揹巕夞楬偱偼屄乆偺晹昳偺徚旓揹椡偲壏搙偺娗棟偑偲偰傕廳梫偱偡丅摿偵丄敿摫懱偼壏搙偵傛偭偰摿惈偑曄壔偡傞偺偑晛捠側偺偱丄崅壏偵側傞傛偆側応崌乮杮婡偱偼峫椂晄梫偱偡乯偵偼丄壏搙摿惈偺専摙傕偟側偗傟偽側傝傑偣傫丅

亙俛揹尮夞楬偺廋惓亜

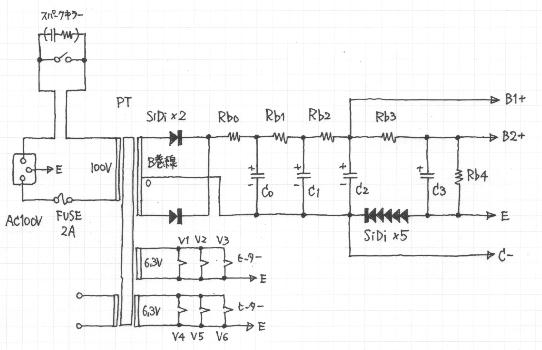

弶抜偑捛壛偝傟丄僪儔僀僶抜偺摦嶌忦審偑曄壔偟偨偙偲偱丄傾儞僾杮懱偺俛揹尮夞楬偵傕庒姳偺廋惓偑惗偠傑偡丅塃恾偼丄杮僾儘僕僃僋僩偱愝寁丒惢嶌偟偨俀抜峔惉偺慡抜嵎摦僾僢僔儏僾儖丒傾儞僾偺婎杮夞楬偱偡丅

俀抜峔惉偺慡抜嵎摦僾僢僔儏僾儖丒傾儞僾偺婎杮夞楬偱偼丄B1+偑弌椡抜偺揹尮偱丄B2+偑弶抜偺揹尮偵側偭偰偄傑偡丅俁抜峔惉壔偟偨応崌丄弌椡抜偺揹尮偼曄峏偁傝傑偣傫偑丄B2+偼僪儔僀僶抜偍傛傃弶抜椉曽偺揹尮偵曄峏偝傟傑偡丅

偲偙傠偱丄俀抜峔惉偺帪偺弶抜偺慡徚旓揹棳乮嵍塃椉僠儍僱儖崌傢偣偰乯偼2mA偱偟偨丅偟偐偟丄俁抜峔惉壔偟偨応崌偼丄弶抜慡懱偱5.2mA偁傝丄偦傟偵壛偊偰僪儔僀僶抜偱8mA乮亖2mA亊4乯傪徚旓偟傑偡偺偱丄慡懱偱13.2mA偵傕側傝傑偡丅

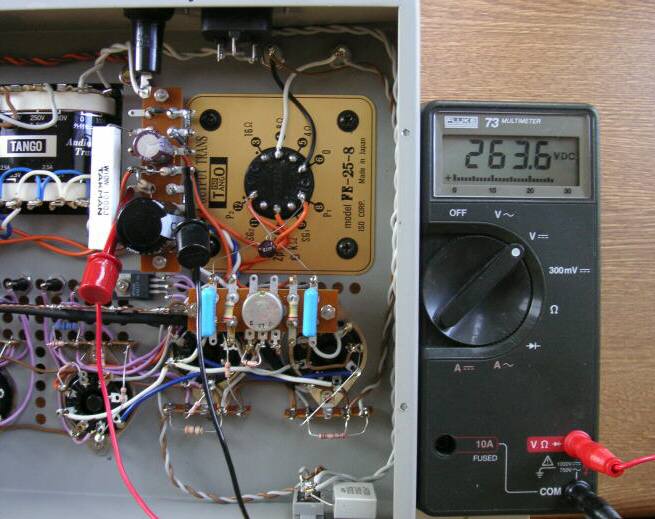

偦偙偱丄夵憿慜偺庤帩偪偺傾儞僾偺B1+偺揹埑偑偳傟偔傜偄側偺偐挷傋偰傒傑偟偨乮塃壓夋憸乯丅僥僗僞乕偱應偭偰傒傞偲263乣264V弌偰偄傑偟偨乮偙偺傾儞僾偼僾儗乕僩揹棳傪庒姳懡傔偵偟偰偄傞偺偱杮偺僨乕僞傛傝傕庒姳掅傔偱偡乯丅偙偙偐傜尰忬偺栺2.5mA偱偼側偔偰13.2mA傪庢傝弌偟偰240V傑偱棊偲偦偆偲偄偆傢偗偱偡丅

B1+偐傜B2+傊偺僪儘僢僾偺偨傔偺掞峈乮Rb3乯偼丄埲壓偺幃偱媮傑傝傑偡丅

B1+偐傜B2+傊偺僪儘僢僾偺偨傔偺掞峈乮Rb3乯偼丄埲壓偺幃偱媮傑傝傑偡丅

乮263乣264V亅240V乯亐13.2mA亖1.74乣1.82k兌偦偟偰丄偙偺掞峈婍偺徚旓揹椡偼丄

乮263乣264V亅240V乯亊13.2mA亖304乣317mW偲側傝傑偡丅掞峈抣偼1.8k兌偱丄揹椡梕検偼梋桾傪傒偰2W宆偑偪傚偆偳偄偄偙偲偵側傝傑偡丅傒側偝傫偺傾儞僾偱偼偳傟偔傜偄偺掞峈抣偑揔愗偐偼偛帺恎偱寁嶼偟偰傒偰偔偩偝偄丅偪側傒偵巹偺応崌丄庤尦偵2k兌2W宆偑偁偭偨偺偱偦傟傪巊偄傑偟偨丅

側偍丄僪儘僢僾揹埑偑掅偔偰Rb3偺抣偑470兌埲壓偵側偭偰偟傑偆傛偆偱偟偨傜丄470兌埲壓偵偼偟側偄曽偑偄偄偱偟傚偆丅儕僾儖彍嫀岠壥偑側偔側偭偰偟傑偄傑偡丅彮乆偺揹埑岆嵎乮亇15V偔傜偄乯偼婥偵偟側偔偰戝忎晇偱偡丅

亙俛揹尮夞楬偺廳梫側廋惓亜

僟僀僆乕僪傪巊偭偨儅僀僫僗揹尮傪巊偭偨夞楬偱俁抜壔偟偨応崌丄壗恖偐偺曽偐傜乽揹尮僗僀僢僠傪愗傞偲丄僽僣僽僣僽僣偲偄偆僲僀僘偑弌傞乿偲偄偆曬崘偑偁傝傑偟偨丅偙傟偼儅僀僫僗揹尮儖乕僩傪宱桼偟偰挻掅堟敪怳偑婲偒偨偨傔偱丄偙傟傪夞旔偡傞偵偼乽5杮偺僟僀僆乕僪偲暲楍偵470乣1000兪F/10V偔傜偄偺僐儞僨儞僒傪捛壛乿偟偰偔偩偝偄丅

僸乕僞乕揹棳偺栤戣

俁抜峔惉壔傪偡傞偨傔偵偼丄6SL7GT偁傞偄偼6SC7傪6SN7GT偵曄峏偟側偗傟偽側傝傑偣傫丅偦偙偱僸乕僞乕揹棳偺栤戣偑惗偠偰偒傑偡丅6SL7GT偁傞偄偼6SC7偺僸乕僞乕婯奿偼丄6.3V丄0.3A偱偡偑丄6SN7GT偼6.3V丄0.6A偲僸乕僞乕揹棳偑2攞偱偁傞偨傔丄僸乕僞乕揹棳偺崌寁偼0.6A憹壛偟傑偡丅6AH4GT丄6L6懓丄EL34偦傟偧傟偺応崌偺僸乕僞乕揹棳偺曄壔偺條巕傪壓昞偵傑偲傔傑偟偨丅

6AH4GT嵎摦PP偺応崌擮偺偨傔偵丄揹尮僩儔儞僗偺僸乕僞乕揹棳梕検傪僠僃僢僋偟偰偔偩偝偄丅偪側傒偵丄PH-185傪巊梡偟偰EL34嵎摦PP偲偟偨応崌丄PH-185偺6.3V姫偒慄偡傋偰傪暲楍偵偟偨帪偺揹棳梕検偼丄2.5A亄2.5A亄2A亖7A偱偡偐傜丄6SN7GT偵曄峏偟偨帪揰偱0.2A偺梕検僆乕僶乕偵側傝傑偡丅偟偐偟丄偁偊偰掕奿僆乕僶乕傪彸抦偱巊梡偡傞偙偲偵偟傑偡丅

俀抜峔惉 俁抜峔惉 6SL7GT or 6SC7 0.3A亊2亖0.6A 6SN7GT 0.6A亊2亖1.2A 6AH4GT 0.75A亊4亖3.0A 6AH4GT 0.75A亊4亖3.0A 崌寁 3.6A 崌寁 4.2A 6L6/6L6GC/5881嵎摦PP偺応崌

俀抜峔惉 俁抜峔惉 6SL7GT or 6SC7 0.3A亊2亖0.6A 6SL7GT or 6SC7 0.6A亊2亖1.2A 6L6/6L6GC/5881 0.9A亊4亖3.6A 6L6/6L6GC/5881 0.9A亊4亖3.6A 崌寁 4.2A 崌寁 4.8A EL34嵎摦PP偺応崌

俀抜峔惉 俁抜峔惉 6SL7GT or 6SC7 0.3A亊2亖0.6A 6SN7GT 0.6A亊2亖1.2A EL34 1.5A亊4亖6.0A EL34 1.5A亊4亖6.0A 崌寁 6.6A 崌寁 7.2A

偦偺崻嫆偼丄PH-185偺3偮偺6.3V姫偒慄偼2A僞僢僾傕2.5A僞僢僾偲摨偠懢偝偺儚僀儎乕偑巊梡偝傟偰偄傞偙偲偑傢偐偭偰偄傞偐傜偱偡丅姫偒慄帺懱偼2.5A偺愽嵼梕検偑偁傞傛偆偱偡偑丄僩儔儞僗慡懱偺揱払揹椡乮VA乯偺忋尷偐傜2A偲惂尷偝傟偨偺偱偼側偄偐偲巚偄傑偡乮恀憡晄柧乯丅偟偐偟丄5V丄3A姫偒慄傪巊偭偰偄傑偣傫偺偱僩儔儞僗慡懱偺惂尷偵偼傑偩梋桾偑偁傞偨傔丄偙偺傛偆側儖乕儖堘斀傕壜擻偵側偭偰偄傑偡丅

憤崌棙摼偲晧婣娨偺愝寁

晧婣娨偵偮偄偰丄俀抜峔惉偐傜俁抜峔惉偵曄峏偡傞嵺偵峫偊側偗傟偽側傜側偄億僀儞僩偵偮偄偰愢柧偟傑偡丅

乮侾乯埵憡偑斀揮偡傞

僇僜乕僪僼僅儘儚夞楬側偳偺椺奜傪彍偄偰丄憹暆夞楬偱偼丄侾抜偛偲偵埵憡偑斀揮偡傞偲偄偆惈幙偑偁傝傑偡丅僌儕僢僪傪僾儔僗偵怳傞傛偆側怣崋偺僒僀僋儖偑偼偄偭偨帪丄僾儗乕僩懁偵尰傟傞憹暆偝傟偨怣崋偺僒僀僋儖偼儅僀僫僗偵怳傟傞傛偆側摦偒傪偟傑偡丅偙偺傛偆側夞楬偺偙偲傪乽斀揮夞楬乿偁傞偄偼乽斀揮憹暆婍乿偲偄偄傑偡丅俀抜偩偲俀夞斀揮偡傞偺偱尦偵栠傝丄俁抜偩偲斀揮偟傑偡丅偦偺偨傔丄俀抜峔惉偐傜俁抜峔惉偵曄峏偟偨帪偵丄晧婣娨傪栠偡懁偑擖傟懼傢傞偺偱偡丅

俀抜峔惉傪俁抜峔惉偵曄峏偟偨嵺偵丄晧婣娨偺偐偗偐偨偑偳偆曄壔偡傞偐傪昞偟偨偺偑壓恾偱偡丅弌椡僩儔儞僗偺俀師懁僗僺乕僇抂巕乮8兌乯懁偼曄峏偁傝傑偣傫偑丄栠偡弶抜懁偑忋壓擖傟懼傢偭偰偄傑偡丅廬偭偰丄傒側偝傫偺傾儞僾傪夵憿偡傞応崌傕丄俀抜峔惉偺帪偵6SL7GT偁傞偄偼6SC7偺偳偪傜懁偺儐僯僢僩偺僌儕僢僪偵晧婣娨傪栠偟偰偄偨偺偐乽報乿傪偮偗偰偍偒丄俁抜峔惉壔偟偨応崌偼丄乽報乿偑偮偄偰偄側偄懁偵晧婣娨傪栠偝側偗傟偽側傝傑偣傫丅

乮俀乯夞楬偑晄埨掕偵側傝傗偡偔側傞

傾儞僾偼丄抜悢偑憹偊傞偵廬偭偰挻掅堟抂偲挻崅堟抂偵偍偄偰埨掕搙偑掅壓偟傑偡丅嵟傕埨掕偟偰偄傞偺偑扨抜偱埨掕偟偰懡検偺晧婣娨傪偐偗傞偙偲偑偱偒傑偡丅俀抜偵側偭偰傕傑偩偐側傝埨掕偟偰偄傑偡偑丄俁抜偵側傞偲晄埨掕偝偑昞柺壔偟偰偒傑偡丅嵎摦夞楬傪巊梡偟偨傾儞僾偱偼丄挻掅堟偺埨掕搙偼婥偵偟側偔偰椙偄偺偱偡偑丄挻崅堟偺埨掕搙偼懠偺曽幃偺傾儞僾偲摨條偵拲堄偑偄傝傑偡丅

偦偺偨傔偺挷惍偺偙偲傪堦斒偵乽埵憡曗惓乿偲偄偄傑偡丅埵憡曗惓偵偼偝傑偞傑側庤朄偑偁傝傑偡偑丄埖偄偑梕堈偱壒偺僋僅儕僥傿傪懝偹偵偔偄旝暘宆傪嵦梡偟傑偡丅曽朄偼丄晧婣娨掞峈偵揔愗側帪掕悢傪帩偨偣偨僐儞僨儞僒傪暲楍偵書偐偣傑偡丅崱夞偺夵憿偱偼丄2.2k兌偺晧婣娨掞峈偵懳偟偰330pF偺僐儞僨儞僒側偺偱丄帪掕悢偼0.726兪S乮亖330pF亊2.2k兌乯丄廃攇悢偵抲偒姺偊傞偲219kHz偱偡丅幚嵺偵偳傫側摿惈偵側偭偨偐偼丄應掕偲挷惍偺復偱徻偟偔弎傋傑偡丅

傾儞僾晹慡夞楬恾丒丒丒嵟廔斉

尰嵼偺巹偺庤尦偵偁傞俀抜峔惉壔偝傟偨夞楬偱偡丅弌椡娗偼俁嬌娗偲偟偰昤偐傟偰偄傑偡偑丄幚嵺偼EL34側偺偱僾儗乕僩乣僗僋儕乕儞丒僌儕僢僪娫偼100兌偺掞峈偱偮側偑傟偰偄傑偡丅奺晹偺揹埑偼丄CRD傗ZD偺偽傜偮偒傕峫椂偟偰斖埻偱昞婰偟偰偄傑偡丅揹尮夞楬偼丄B2+乮240V乯偵棊偲偡偨傔偺掞峈偑2k兌 2W宆偵曄峏偵側偭偨偩偗偱丄偦傟傛傝忋棳偼尦偺傑傑偱偡丅弌椡抜傕偝傢偭偰偄傑偣傫丅